**Computer Architecture**

| <b>Course De</b>                                                         | sign Committee                                                               |                  |          |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|----------|

| <b>Prof. Ashutosh G</b><br>Director (In-charge                           | upta                                                                         | JPRTOU Allahabad | Chairman |

| <b>Prof.</b><br><b>Member</b><br>Department of CSI<br>MNNIT Allahabad    |                                                                              | eta              | Agarwal  |

|                                                                          | <b>Upendra</b><br>r, Department of Computer S<br>ayaya Gorakhpur University, |                  | Tripathi |

| <b>Dr.</b><br><b>Member</b><br>Associate Professo<br>University of Allah | Ash<br>r, Department of Computer S<br>nabad, Prayagraj                       |                  | Khare    |

|                                                                          | r (Computer Science)<br>UPRTOU Allahabad                                     |                  | Member   |

|                                                                          | ar <b>Balwant</b><br>(Computer Science)<br>UPRTOU Allahabad                  |                  | Member   |

| Course Pro                                                               | eparation Comm                                                               | ittee            |          |

| <b>Dr. Brajesh Kum</b><br>Associate Professo<br>Departement of CS        | ar<br>r                                                                      |                  | Author   |

| · •                                                                      | <b>Singh</b><br>nent of Computer Science En<br>edkar University, Agra        | gineering        | Editor   |

| Mr.Manoj<br>Coordinator<br>Assistant Professor                           | <b>K</b> (computer science),                                                 | umar             | Balwant  |

Assistant Professor (computer science), School of Sciences, UPRTOU Allahabad

# **Bachelor of Computer** Application

Uttar Pradesh Rajarshi Tandon

BCA-EC Open University

Block

# 1

**PROCESSOR BASICS**

Unit 1 CPU Organization Unit 2 Data Representation

Unit 3

**Instruction Sets**

## **BLOCK INTRODUCTION**

This block deals with the basic concepts of computer architecture. It provides the insight into fundamentals of computer organization, data representation, and instructions. The block is divided into three units: Unit 1, Unit 2, and Unit 3. The Unit 1 discusses the evolution of computer systems with emphasis on technological development, processing, storage, etc. The development of computers from the first generation to the fifth generation is presented. The central processing unit and its major components are explained. Unit 2 introduces the number systems and different number representations. The methods of conversion from one number system to other number systems are explained. Unit 3 explains how the computer system is given commands with the help of computer instructions. The computer instruction formats and their memory representation are discussed.

### **UNIT-1 CPU Organization**

#### Structure

- 1.0 Introduction

- 1.1 Objectives

- 1.2 First Generation Computers

- **1.3 Second Generation Computers**

- 1.4 Third Generation Computers

- 1.5 Fourth Generation Computers

- 1.6 Fifth Generation Computers

- 1.7 Central Processing Unit

- 1.8 Bus Organization

- 1.9 Summary

- **Review Questions**

#### **Unit 1: CPU Organization**

#### **1.0 Introduction**

A **computer** is an electronic device that can perform a large range of computational tasks by manipulating data or information. Modern computers are able to **store**, **retrieve**, and **process** data according to the given set of instructions or **program**. The first electronic computers were developed during late 1940s. The early computers were able to perform mainly numerical computations. The modern computer systems are based on binary number system. The numbers in binary system are represented by just two types of digits: 0 and 1. The digits in binary system are called as bit and computers that use binary number system are known as digital computers. Digital computers represent the information in the form of a group of bits. The computer systems evolved over the years witnessing a significant progress in technology.

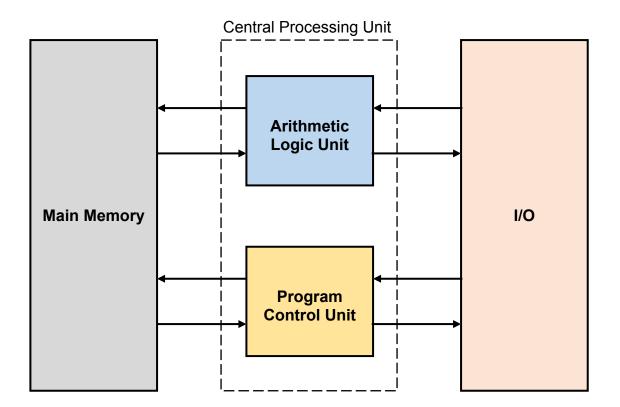

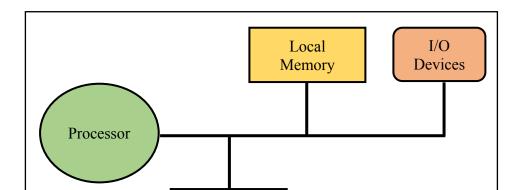

The digital computer systems have three main modules: **Central Processing Unit (CPU)**, Memory, and Input/Output (I/O) systems. Each module contains their internal components. Both memory and I/O systems are connected to CPU through some communication interfaces. All components work collectively to provide the desired results. The CPU acts like a brain of the computer, which carries out the most of operations and data manipulation. The memory provides storage for the data and instructions. The CPU can access the data and instruction from the memory. The I/O system consists of various input and output devices including keyboards, printers, mouse, and camera, etc. These devices are used provide data to and from the users. The **Computer Organization** is concerned with how the different hardware components or operational units in a computer system work and with the way they are linked together. The **Computer Architecture** is concerned with the instruction sets, representation of data types, techniques for memory addressing, methods for I/O operations, etc. The programmers are concerned with the computer architecture, while computer organization deals with low level designing. The computer system executes a set of instructions to perform a particular task. The instructions are grouped in the form of a program. The program performs a variety of operations depending on the algorithm. It needs to process some data during the course of execution. The data could take many different forms from simple to complex structures. It is necessary to store the data in computer system for the processing. The data storage is a highly important requirement for the computer system so that data could be stored and subsequently retrieved when needed. The movement of data is also equally important. Data may originate outside the computer system. It goes into and moves out of the computer system through a set of I/O devices. The movement is done through some communication lines. The various events in the system should be controlled to manage and efficiently utilize the various resources.

#### 1.1 Objectives

The major objectives of this unit are as follows.

- 1. To provide the knowledge on the evolution of computer systems.

- 2. To provide overview on the technological progress of the computers.

- 3. To understand the major modules of the computer system.

- 4. To discuss the basic organization and architecture of computer system.

#### **1.2 First Generation Computers**

World's first electronic computer named as **Electronic Numerical Integrator And Computer (ENIAC)** was developed at University of Pennsylvania by Professor John Mauchly and his student John Eckert in 1946. It was a huge machine occupying 1500 square feet space, weighing around 30 tons, and consuming 140 kilowatts power to operate. It was a decimal machine implemented using more than 18000 **vacuum tubes**. It used 10-digits decimal number and each digit was represented by a group of 10 vacuum tubes. It was capable of performing 5000 additions in a second. ENIAC had to be programmed manually by adjusting cables and switches, which was its major drawback.

The programs of ENIAC were not stored memory. Therefore, it was a tedious job to alter a program as it required to set switches on/off and plugging/unplugging cables.

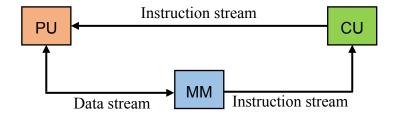

Later, an idea of stored program concept was given by John von Neumann, who was also involved with ENIAC project as a consultant. He proposed an idea of a machine Electronic Discrete Variable Computer (EDVAC) based on stored program concept. John von Neumann developed a new stored program computer named Institute for Advanced Studies (IAS) computer in 1952, which can be considered as a prototype for the modern general purpose computers. The architecture of IAS computer also known as Von Neumann architecture is shown in Figure 1.1 It consists of a main memory that stores both data and instructions, an Arithmetic and Logic Unit (ALU) capable of performing arithmetic and logical operations, a Control Unit (CC) responsible for the interpretation of instruction and causing them to execute, and **Input Output (I/O)** equipment operating under the control unit. The contents of the memory are addressable by location. The instructions are executed in sequential way. IAS computer uses a binary system representing both data and instructions in binary form. Its memory consists of 1000 storage locations called words. Each word contains 40 binary digits. The control unit fetches the instruction from memory causing them to execute sequentially.

#### Figure 1.1: von Neumann structure of computer system

Eckert-Mauchly Computer Corporation developed the first commercially successful computer named **Universal Automatic Computer I (UNIVAC I)**. It was capable of performing matrix algebraic computations and solving statistical and logistical problems. Later **UNIVAC II**, came into the market with larger memory capacity and higher performance in 1950. The major success of the UNIVAC division its 1100 series of computers. However it was intended for scientific applications involving complex and long calculations. IBM launched its first electronic stored-program computer named 701 in 1953, which was also intended primarily for scientific applications. Later IBM introduced 702 and other 700/7000 series computers. Major highlights of the first generation computers are vacuum tubes, magnetic drum memories, and machine language programs. These computers were highly sequential able to solve only one problem at a time. The punch cards and paper tapes were used for input and output was obtained through printouts. These computers were in trend till 1956, when transistor based computers evolved in late 1950s.

#### **1.3 Second Generation Computers**

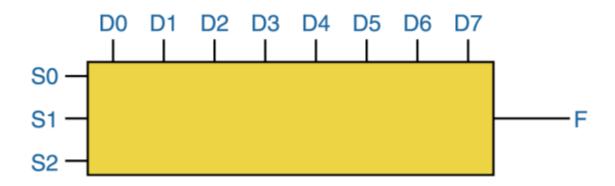

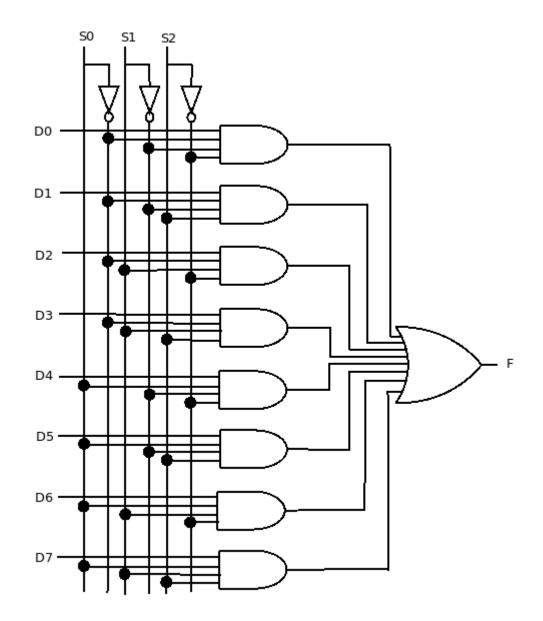

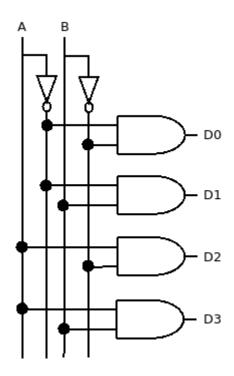

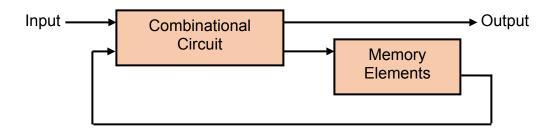

Development of **transistor** in 1947 at Bell Labs was great invention that revolutionized the computer world during late 1950s. The vacuum tubes were replaced by the transistors in electronic computers leading to the rise of second generation of computers. The transistor is a solid-state device, which is smaller in size, lower in cost, and generate lesser amount of heat as compared to vacuum tubes. The use of transistors was the major feature of the second generation computers, although the input and output operations were still performed with the help of punch cards/tapes and print outs respectively. The use of multiplexor is another important highlight of the second generation. The multiplexor allows CPU and data channels to act independently. The computers became much smaller called as mini-computers with better processing speed, larger memory capacity, and more complex ALU and controls units than previous generation computers. The computers moved from binary/machine language to assembly language. Early versions of some high level languages also came into existence in that era. The memory also moved from magnetic drum to magnetic core technology. Digital Electronic Corporation (DEC) product **PDP-1** and **IBM 7094** are the examples of second generation computers.

#### **1.4 Third Generation Computers**

The era of third generation computers witnessed the emerging of microelectronics that significantly reduced the size of the computers and drastically improved the processing and efficiency of the computers. The development of **Integrated Circuit (IC)** was the revolutionary achievement of that era that changed the electronic industry broadly. IC allows to fabricate many components such as registers, transistors, logic gates, and memory cells onto a thin silicon wafer. The keyboards and monitors interfaced with an operating system replaced the punch cards and printouts. The cost of the computers reduced so much that these machine became accessible to mass audience first time. **IBM System/360** and DEC **PDP-8** are the examples of third generation computers.

#### **1.5 Fourth Generation Computers**

In year 1971, Intel developed a chip Intel 4004 that placed CPU, memory, and I/O controls all onto a single chip leading to the birth of microprocessor. The next major breakthrough was the development of **Intel 8008** in 1972. It was the first 8-bit microprocessor. Later in 1974 Intel introduced its first general purpose microprocessor Intel 8080. Like Intel 8008, Intel 8080 was also a 8-bit processor but it was faster having more rich instruction set, and larger addressing capabilities. By the end of 1970s, the 16-bit microprocessor also began to appear. One such processor was **Intel 8086**. The journey continued and a number of 16-bit to 64-bit processors were developed in subsequent years including **Pentium**, **Pentium Pro**, **Pentium II**, **Pentium III**, **Pentium**

**IV**, **Core2Duo**, and **Core2Quad**, etc. During that period the microprocessors came out of the realm of computers and microprocessors began to use in home appliances and other everyday products. Apple introduced the **Macintosh** operating system in 1984 that gained popularity with Apple devices. The increasing processing power of small computers lead to the computer networks that ultimately gave birth to **Internet**. The use of **Graphical User Interface (GUI)** based software, use of mouse, and development of laptops and other hand-held devices were the major advances of this era.

#### **1.6 Fifth Generation Computers**

The research and development in the field of microprocessors, memory, I/O controls and other related components of computing devices continues. In recent times Intel produced another revolutionary microprocessors such **i3**, **i5**, **i7**, **i9**, and **Xeon** series processors, etc. with more processing power. This era observed the production of laptops and hand-held devices at economical cost. The machines with high processing power, larger memories, and high storage capacity are now available at affordable prices. The parallel processing with **multi-core** processors and **Graphics Processing Units (GPU)** is thrust of modern computers. Computers have become household commodities. Now computers with artificial intelligence are under development. Quantum computing, Nano technology, and massive parallel processing are the essence of future generation computers.

#### Check your progress 1

- 1. Define a computer system.

- 2. Write the names of three major modules of a digital computer system.

- 3. Differentiate computer organization and computer architecture.

- 4. Write the name of the first electronic computer.

- 5. Write the name of the first commercially successful electronic computer.

- 6. Differentiate UNIVAC I and UNIVAC II.

- 7. What are the major features of the second generation computers?

- 8. What is transistor?

- 9. How is a multiplexor works?

- 10. What is the revolutionary achievement of the era of third generation computers?

- 11. Write two examples of third generation computers.

- 12. Which microprocessor is the first 8-bit microprocessor?

- 13. When did GUI based software appear?

- 14. Write the current generation of the computers.

- 15. What is the thrust of the fifth generation computers?

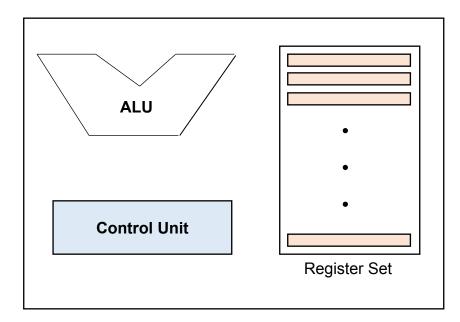

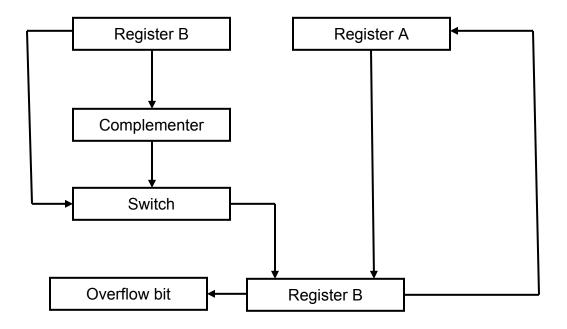

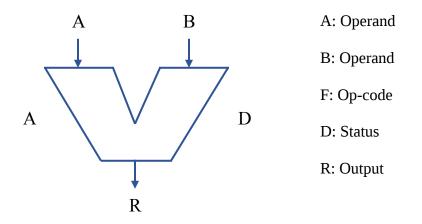

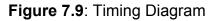

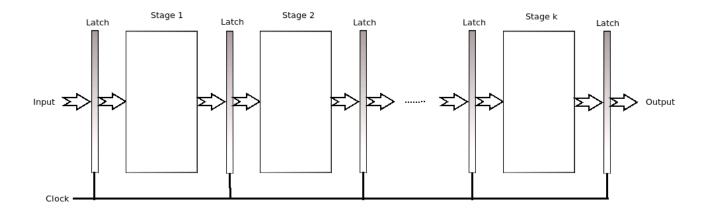

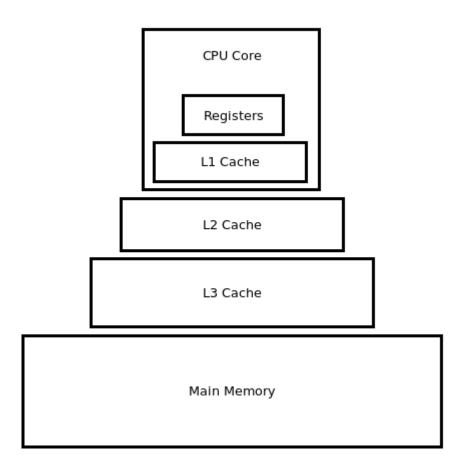

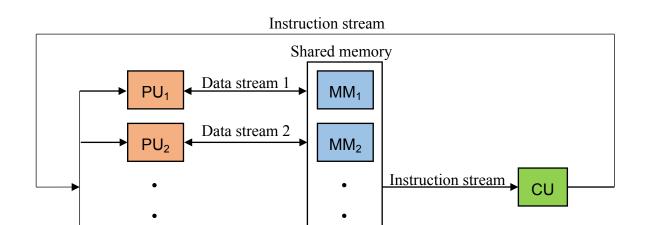

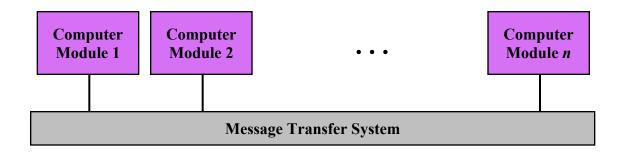

Figure 1.2: Major components of CPU

#### **1.7 Central Processing Unit**

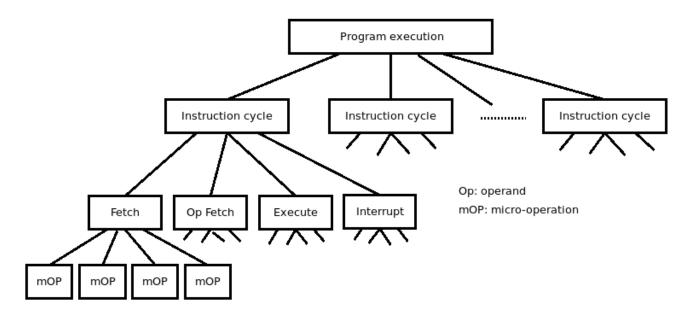

Virtually all contemporary computer design are based on von Neumann architecture as shown in Figure 1.1. A computer consists of three main modules: CPU, memory, and I/O components. Both data and instructions/programs are stored in a single memory. It is a read-write memory whose data/instructions are addressable by their location. These

three modules are interconnected in some way to achieve the program execution. The instructions are executed sequentially unless explicitly specified otherwise. The behaviour of a computer system can be described by explaining the behaviour of each module. In this section, the functions of CPU are discussed. The program execution is actually done by CPU, which reads instructions specified in a program from the memory and executes them. A typical CPU consists of three major components: a set of registers, ALU, and **Control Unit (CU)** as shown in Figure 1.2.

The main functions of CPU are to fetch instructions from memory, decode instructions and execute, read-write data from/to memory, and data transfer from/to I/O devices. Registers are used to hold instructions, memory addresses, and other kind of data within the CPU. ALU is mainly concerned with the execution of arithmetic and logical operations. CU is responsible for providing directions to ALU, memory, and I/O systems to respond to the instructions. The CPU can be divided into two sections: data section and control section. Data section contains registers and ALU. Control section basically contain control unit only. Data section performs operations on data elements and control section issues signals to control the flow of data.

#### 1.7.1 Register Set

The registers are extremely fast memories within CPU that are used to temporarily hold the data. The number and type of registers vary from computer to computer. During the execution of an instruction, the CPU needs to read and store intermediate results into memory. But the data transfer between CPU and memory is time consuming as memory is too slow compared to processor. Therefore, it is convenient to store intermediate results in processor registers during the operation. There are different types of registers that are used for different purposes.

General Purpose Registers are multipurpose registers that can store both data elements and memory addresses. Programmers can use general purpose registers in a variety of ways. There are four general purpose registers in Intel 8086 microprocessor: AX, BX, CX, and DX. The description of four general purpose registers is as follows. AX: Known as accumulator register, it is preferred for the most of the operations. BX: Known as base register, it is used to store memory address. CX: Known as count register, it is used in looping.

DX: Known as data register, it is used for multiplication and division operations.

Each of these registers can be used as two 8-bit registers or a single 16-bit register. Eight high-end bits (high-end byte) are referred as AH and eight low-end bits (low-end byte) are referred as AL for register AX as shown in Figure 3. Other three registers are also work in the same manner. Modern 32-bit Intel processors have eight general purpose registers while there are 16 such registers in 64-bit Intel processors.

**Memory Access Registers** are needed for memory read/write operations. These registers are used by CPU exclusively and are not directly available for the programmers. For each memory read/write operation, two registers are required: **Memory Data Register (MDR)** and **Memory Address Register (MAR)**. MDR is used to hold the data to store/fetch into/from memory and MAR keeps the address of the memory location.

AX: 15 0 AH 8 AL BX: 15 BH 8 BL 0 CX: CH 0 15 8 CL DX: 15 DH 8 DL 0

#### Figure 1.3: Use of single 16-bit register as two 8-bit registers

Instruction Fetching Registers are used in the instruction fetch operation. There are two main registers namely Instruction Register (IR) and Program Counter (PC) used to fetch the instructions from the memory. IR is used to store the fetched instruction and PC contains the address of memory location of the next instruction to fetch. PC is updated after each successful fetch operation. A special register known as Program Status Word (PSW) is used to maintain status information of the executing program. The bits of PSW are set by the CPU to indicate the current status. In addition some Condition Registers and Control Bits/Flags are also used to maintain the status of the program.

The flags are as follows.

Aux Carry: Set if there is a carry from bit 3 to bit 4

**Carry**: Set if the last unsigned arithmetic operation had a carry

Direction: Used for block transfer of data

Interrupt: Set to enable/disable interrupt

Overflow: Set if the last signed arithmetic operation overflowed

Parity: Used for a parity check

Sign: Set if the result of last arithmetic operation is negative

Trap: Set after each instruction if CPU should halt.

**Zero**: Set if the result of last arithmetic operation is zero

There are set of **Special Purpose Registers** that are used to load only specific information. **Index Register (IR)** contains offset from a segment register for the operand that need to fetch. The contents of IR are added to the segment register to obtain the memory address of the operand. There are four **Segment Pointers** known as **Code Segment (CS)**, **Data Segment (DS)**, **Stack Segment (SS)**, and **Extra Segment (ES)** that contain base locations for program instructions, data elements, or stack. CS is used to hold base location of program code, DS contains base location for variables, base location of the stack is loaded in SS, and ES is an additional register for the base location of the variables. **Stack** is a data structure in which last element stored is

retrieved first. A register known as **Stack Pointer** is used to indicate the top of the stack. When a data element is stored in the stack, the stack pointer is incremented/decremented depending on whether stack grows up/low in memory.

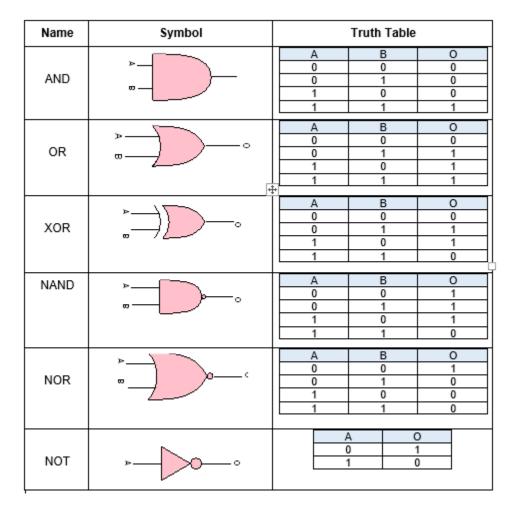

#### 1.7.2 Arithmetic Logic Unit

Arithmetic Logic Unit (ALU) is an electronic component that is implemented using logic devices. The logic devices are capable of storing binary digits and perform Boolean operations. It performs the arithmetic, logical, and related operations. The major arithmetic operations are addition, subtraction, multiplication, and division. The major logical operations are AND, OR, and NOT, etc. ALU is connected to other components of the CPU that are supposed to provide the data to it, where desired operations are performed and results are sent back. The data elements are sent to ALU by writing values to its registers. All information is stored in binary form. The operations are performed using transistor switches and by connecting multiple transistors. The results are also provided by storing the data in registers. ALU may also provide the results by setting the flags.

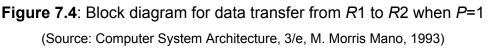

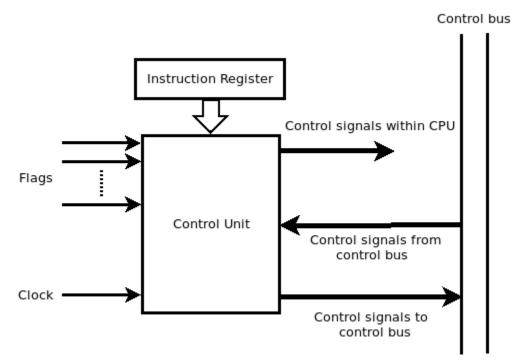

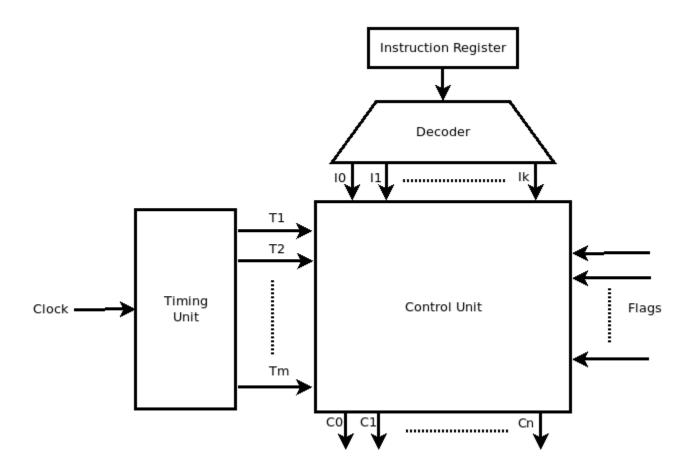

#### 1.7.3 Control Unit

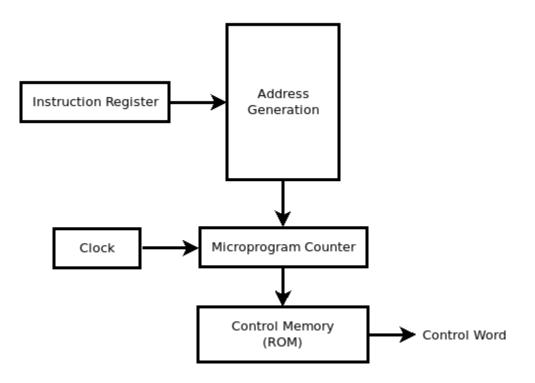

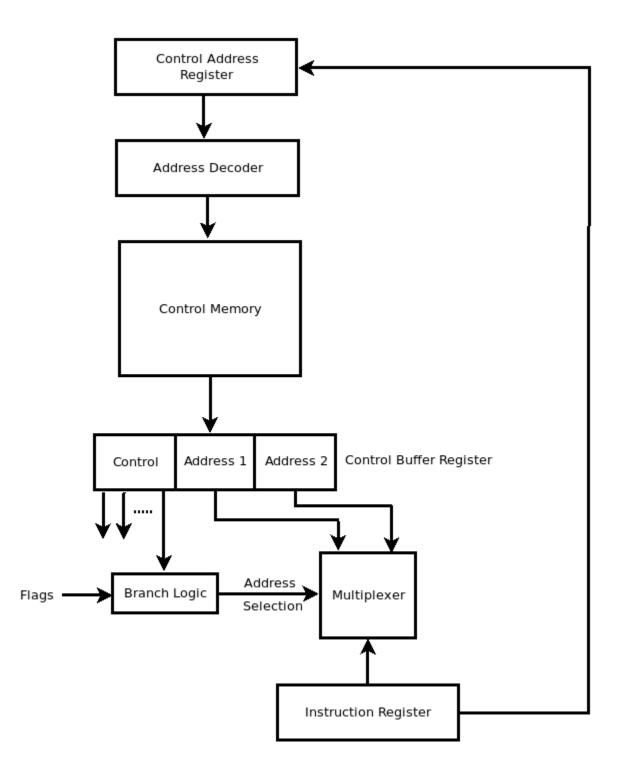

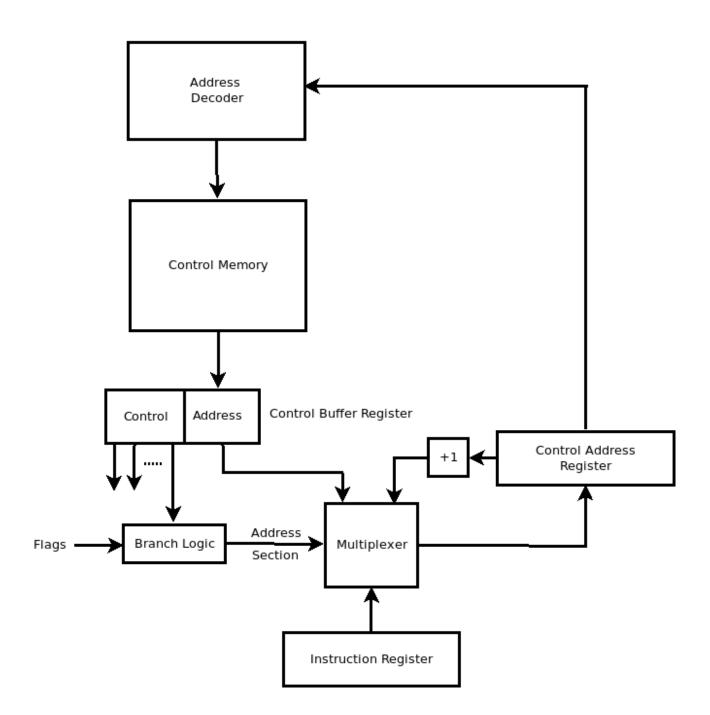

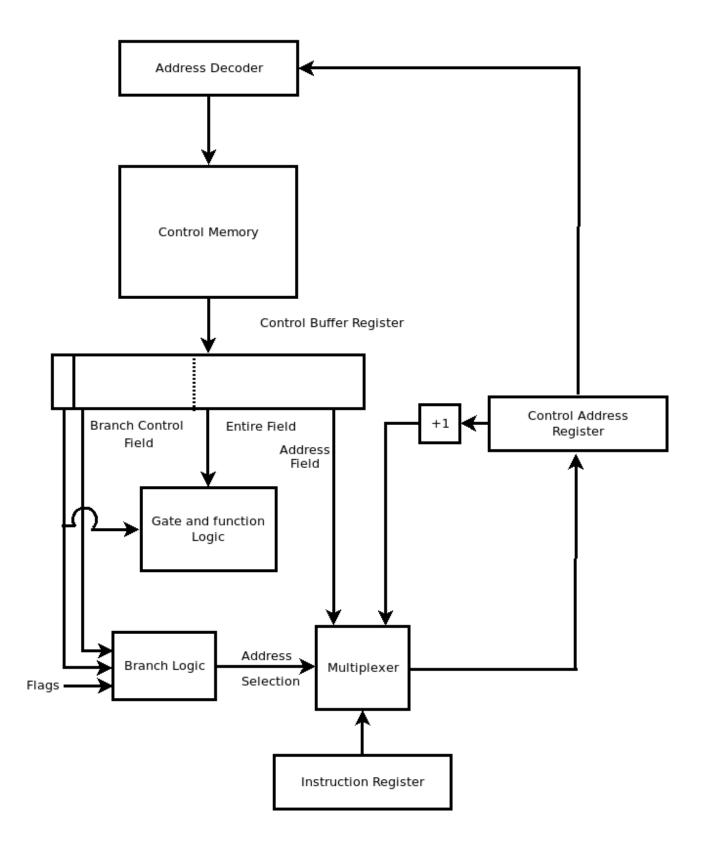

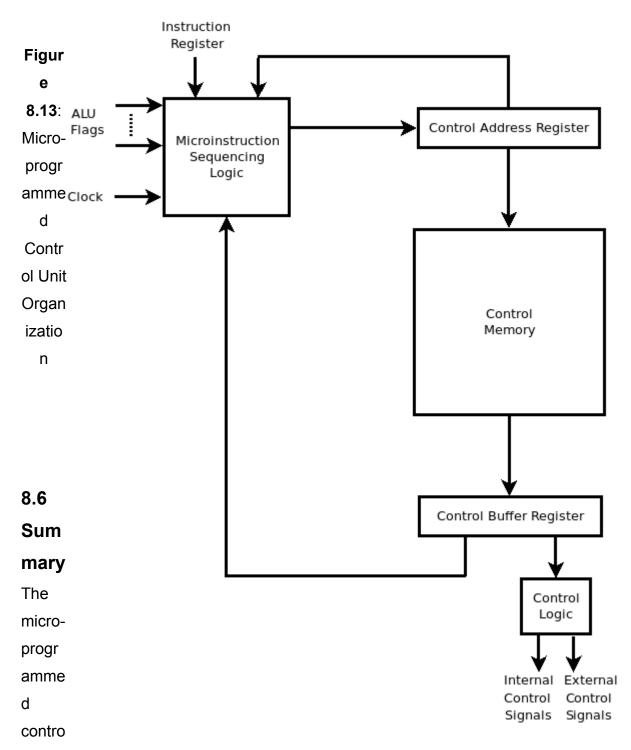

The actions of CPU are controlled by the Control Unit (CU), which issues micro-orders to CPU and I/O systems. The micro-orders are sent in the form of control signals over dedicated control lines. The flow of data between CPU and other units is controlled by the CU. There are two different types of CU: hardwired and micro-programmed. In a hardwired CU, the control signals are generated by fixed logic circuits. On the other hand in micro-programmed CU, the controls signals are stored in a special memory called **control memory** in the form of microinstructions. The control memory is not accessible to the users or programmer. A sequence of microinstructions is called micro-program that is stored in control memory. The hardwired CU is faster and economical than micro-programmed CU. But micro-programmed CU can easily adapt to the changes in the system.

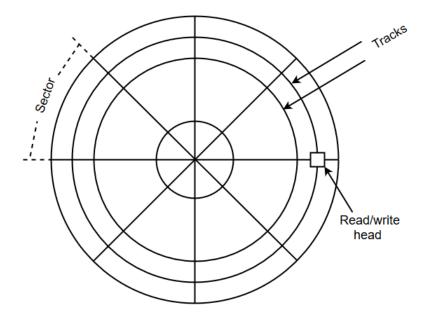

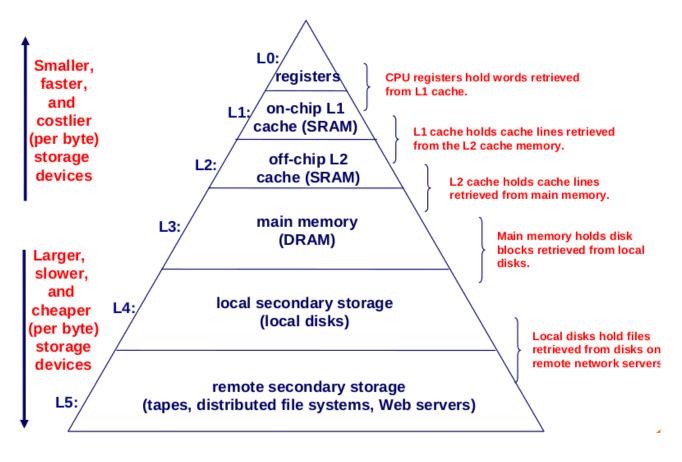

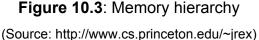

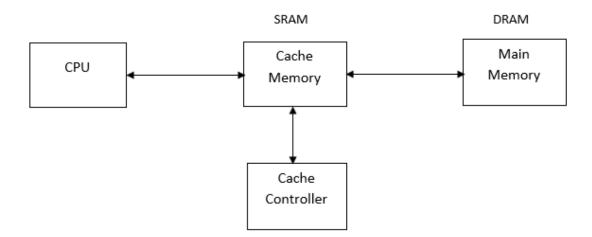

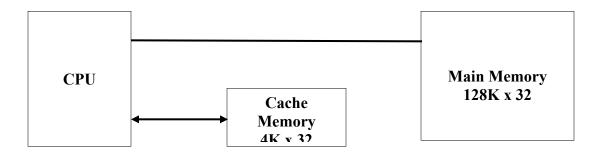

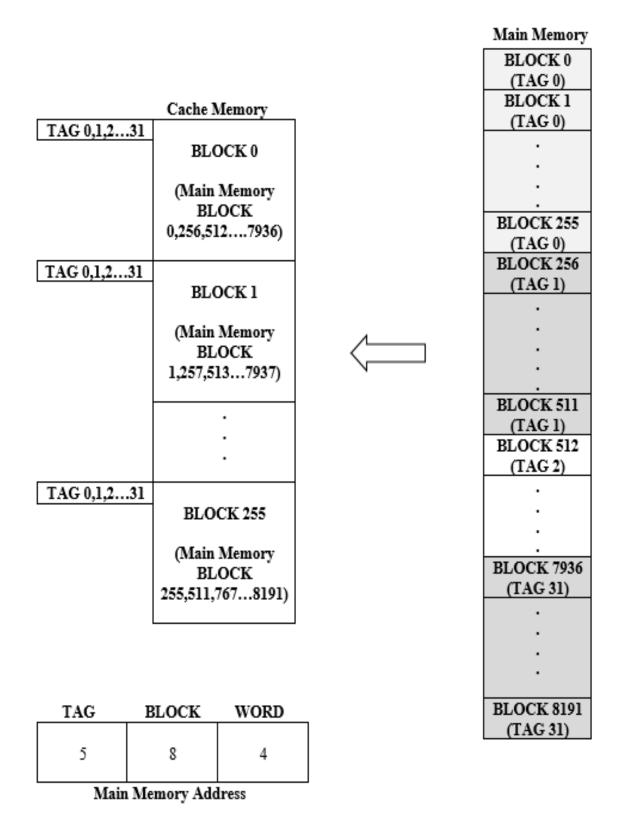

#### 1.8 Memory

Memory is another important component of the digital computer system. It is required to store program and related data. The data and program instructions are transferred between memory and processor during the operation. The memory is an expensive component and often it is not large enough to accommodate the entire program and data. But not all the information is required by the processor at the same time. Therefore, a small memory can support a larger program with the help of a low-cost backup storage. The programs and data are kept in backup storage. Only the currently required programs or data are brought in memory from the backup storage as per need. The low-cost storage are larger in capacity but slower in speed. It is important to make a balance among speed, size, and cost of the memory. Therefore, a combination of different types of memory devices are used in the computer system. Different memories vary in their characteristics and several attributes. A relatively fast storage unit is known as the primary or main memory of the system. The main memory is volatile in nature that loses the entire data when there is no power. It cannot store the data permanently. While the low-cost backup storage is known as the secondary memory. The secondary memory is slow in speed but it can store the data permanently even in the absence of the power. The technology used to access the data from the storage is also different in different memories that will be discussed later in subsequent units.

#### 1.9 I/O System

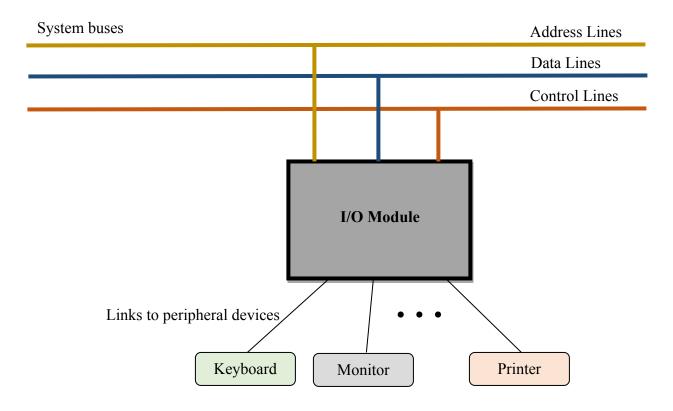

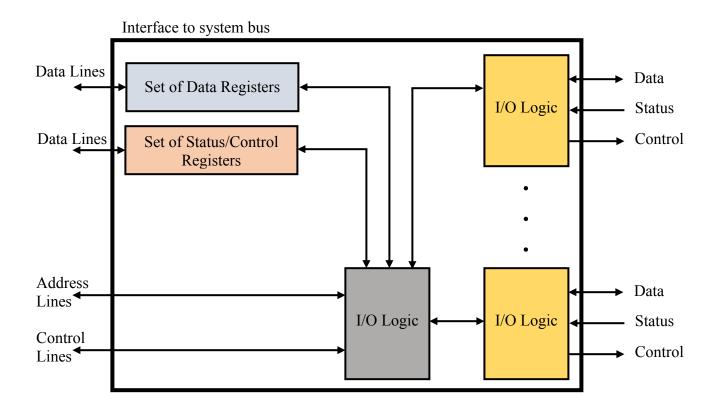

I/O devices in a computer system are required to perform fundamental input output operations. The I/O devices are a medium of communication between computer system and outside world. The I/O devices are also known as peripheral devices. The most common devices are keyboard, mouse, printer, and display units, etc. The peripheral devices communicate with CPU through communication lines. The peripheral devices are too slow as compared to the CPU. Therefore, for the proper functioning of the system a synchronous mechanism is required.

An interface unit is associated with each peripheral device that receives the command and control signals from I/O bus. The I/O bus connects the processor to interfaces of all the peripheral devices. The processor issues the commands to the peripheral devices that are decoded and interpreted by the interface. There are different

types of commands such as control, status, data input, and data output commands that can be issued to a device. A control command is used to activate the peripheral device and inform it to perform the specific operation. The status command is issued to test the device status condition. A device could be in various status conditions such as ready, busy, and error, etc. In case of data input command, the data is transferred from the device to the I/O bus. While, data output command causes the data transfer from I/O bus to the device. The peripherals not only communicate with processor but they also communicate with the main memory. A separate bus is used between memory and peripherals.

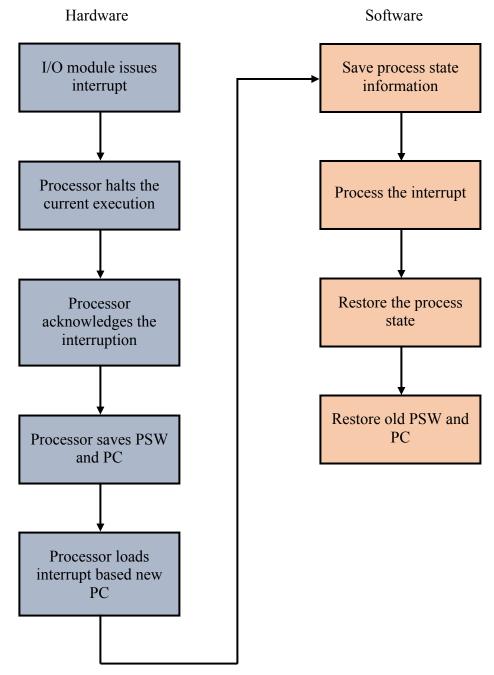

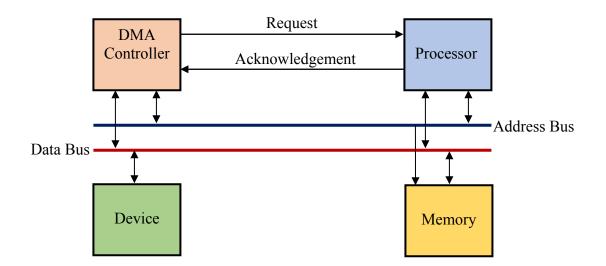

Data transfer between peripherals and CPU could performed in different modes including Programmed I/O, Interrupt-initiated I/O, and Direct Memory Access (DMA). In programmed I/O, the data transfer is done with the help of a program and CPU takes active part in the operation. It results in loss of useful CPU cycles. In interrupt based approach, the CPU does not continuously involved in the data transfer, instead it initiates the process and goes back to its normal work. In DMA, the data transfer takes place between I/O devices and memory through memory bus.

#### 1.10 Bus Organization

The data transfer and issuance of control signals between different components of the computer system are performed with the help of system buses. A system bus is a group of wires or printed circuits that permits bidirectional communication among the different components of computer. A system bus may have 50 to 100 communication lines. The system buses can broadly be divided into three categories: data buses, address buses, and control buses. Data buses carry data elements, address buses provides memory address to place the data, and control buses carry control signals between CU and other components of CPU. There are three different types of bus organizations used in computer systems: one-bus, two-bus, and three-bus organizations. The one-bus organization makes use of one bus for the incoming and outgoing data between registers. Single bus can carry only one operand or data element during a clock cycle. Therefore, for the operations that need two operands, two clock cycles are required to fetch the data. The one-bus organization is the most simple and the least expensive but

it slows down the performance of the system as it can transfer only one data element in a cycle. In the two-bus organization, the general purpose registers are connected to two buses. Whenever, there is a need of two operands, both operands can be transferred at a time. The two-bus organization is faster but expensive also than one-bus organization. The three-bus organization uses two buses to move data to the registers and one bus is used for transferring the output from the registers. By using more buses, more data can be transferred at a time, but it also increases the cost of the system.

#### Check your progress 2

- 1. List the main modules of a computer system.

- 2. What are the main functions of CPU?

- 3. Write the major components of CPU.

- 4. What is the role of ALU in CPU?

- 5. What is a register?

- 6. List the general purpose registers in Intel 8086.

- 7. What kind of information is stored in MDR and MAR?

- 8. What is program status word?

- 9. How many types of control unit are there? Write the names of different control units.

- 10. Differentiate primary memory and secondary memory.

- 11. What is the role of interface unit in I/O system?

- 12. List the different data transfer modes for I/O devices.

#### 1.11 Summary

Modern computers evolved after the continuous technological advancements through different generations. Each generation of computers has a hallmark technology from vacuum tubes to multi-core processors that revolutionized the contemporary era. However, the most of computer systems are based on von Neumann architecture proposed by John von Neumann several decades ago. According to von Neumann architecture, the computer systems have three main modules: CPU, memory, and I/O

systems. The CPU further has three main components: ALU, CU, and a set of registers. The most of the arithmetic and logical operations are carried out by ALU and CU issues instructions in the form of control signal to different components that act accordingly. The registers are extremely fast memories that temporarily hold the small piece of data during the operations. All components work collectively to complete the operations. The communication with CPU or between CPU and other modules takes place through systems buses.

Memory is another important component of the digital computer system. It is required to store program and related data. The data and program instructions are transferred between memory and processor during the operation. The programs and data are kept in a backup storage. Only the currently required programs or data are brought in memory from the backup storage as per need. A relatively fast storage unit is known as the primary or main memory of the system. The main memory is volatile in nature that loses the entire data when there is no power. While the low-cost backup storage is known as the secondary memory. The secondary memory is slow in speed but it can store the data permanently even in the absence of the power.

I/O devices in a computer system are required to perform fundamental input output operations. The I/O devices are a medium of communication between computer system and outside world. The I/O devices are also known as peripheral devices. The peripheral devices are too slow as compared to the CPU. Therefore, for the proper functioning of the system a synchronous mechanism is required. An interface unit is associated with each peripheral device that receives the command and control signals from I/O bus. The I/O bus connects the processor to interfaces of all the peripheral devices. The processor issues the commands to the peripheral devices that are decoded and interpreted by the interface. The peripherals not only communicate with processor but they also communicate with the main memory. A separate bus is used between memory and peripherals. Data transfer between peripherals and CPU could performed in different modes including Programmed I/O, Interrupt-initiated I/O, and DMA. The involvement of CPU in I/O operations is minimal in case of DMA.

The data transfer and issuance of control signals between different components of the computer system are performed with the help of system buses. A system bus is a group of wires or printed circuits that permits bidirectional communication among the different components of computer. The system buses can broadly be divided into three categories: data buses, address buses, and control buses. Data buses carry data elements, address buses provides memory address to place the data, and control buses carry control signals between CU and other components of CPU. By using more buses, more data can be transferred at a time, but it also increases the cost of the system.

#### **Review Questions**

- Q1. Describe the development of computer systems through different generations with emphasis on hallmark technology for each generation.

- Q2. With the help of a suitable figure, explain the von Neumann architecture.

- Q3. Write main components of CPU with their major functions and describe CPU organization with the help of a figure.

- Q4. How many types of registers are there in register set of CPU? Explain utility of different registers.

- Q5. What is system bus? Write different bus organization with their important features.

- Q6. A computer system consists of different kind of storages. Explain the reason.

- Q7. Why is the I/O system required in a computers system? Explain how data transfer takes place between I/O devices and CPU.

# **Unit 2: Data Representation**

#### Structure

- 2.0 Introduction

- 2.1 Objectives

- 2.2 Number System

- 2.3 Negative Number Representation

- 2.4 Range Extension

- 2.5 Fixed-Point Numbers

- 2.6 Floating-Point Numbers

- 2.7 IEEE Floating-Point Standard

- 2.8 Summary

- **Review Questions**

#### Unit 2: Data Representation

#### 2.0 Introduction

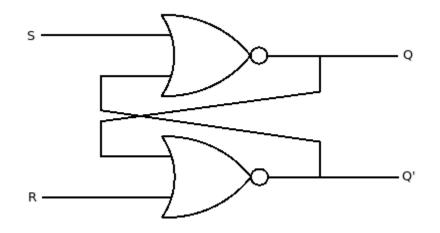

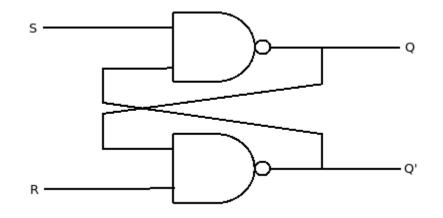

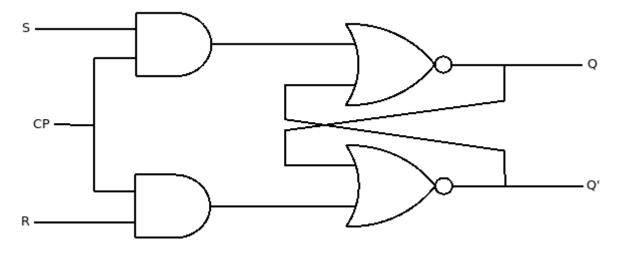

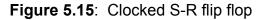

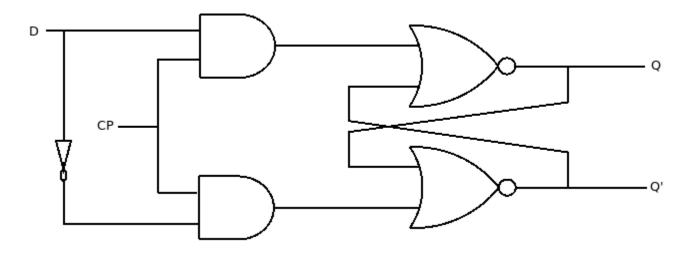

The arithmetic logic unit (ALU) is an important component of the central processing unit (CPU) that performs arithmetic and logic operations on data. The data elements are transferred from memory or I/O devices to ALU for the processing. Data representation refers to the form in which data can be stored, processed, and transmitted. The data presented to ALU are stored in registers. The registers are made of flip-flops, which are two-stage devices. Therefore, binary-coded representation of data is the most suitable for digital computers. There are three major types of data elements used in computer systems: numbers, alphabets, and special characters. All these data elements can be represented in binary-coded form.

A number system with base *r* is a system that uses distinct symbols to represent *r* distinct digits. The base is also known as radix. Other numbers are represented in terms of those *r* digits. For example, the decimal number system having base 10, uses 10 distinct symbols for digits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. All other numbers are the combinations of these 10 digits. Similarly binary number system uses a base 2, octal number system has a base 8, and base or radix for hexadecimal number system is 16. An unsigned integer number *N* can be represented in a base *r* number system using *n* digits as  $(a_{n-1}a_{n-2}...a_1a_0)_r$ ,  $0 \le a_i \le r - 1$ . The binary number system is highly useful for

digital computers. Any data numeric or alphanumeric is internally represented in binary form in a computer system. The software or programmers need to interpret the binary pattern appropriately. The interpretation of binary pattern is called data representation. Other number systems such as decimal number system are also important as users are more convenient with this to perform different types of operations. Sometimes it is necessary to convert a number from one representation to other representation. The numbers in one system can be converted to other number systems with help of some algorithms or methods.

#### 2.1 Objectives

The major objectives of this unit are:

- 1. To acquire basic knowledge of number systems.

- 2. To learn conversion of numbers in one system to the numbers in another system.

- 3. To learn different representations of data.

#### 2.2 Number Systems

The binary number system is the most suitable system for digital computers. There are only two symbols 0 and 1 in binary number system. Each number is represented as string of 0 and 1. There are other number systems such octal and hexadecimal. In octal number system, eight different digits 0, 1, 2, 3, 4, 5, 6, 7 are used to represent the numbers. On the other hand, in hexadecimal representation sixteen different digits 0, 1, 2, 3, 4, 5, 6, 7 are used to represent the numbers. On the other number systems using **Radix Conversion** method. To convert a converted to other number systems using **Radix Conversion** method. To convert a number representation in base (or radix)  $b_1$  to another number system with base  $b_2$ , the number is successively divided by  $b_2$  and remainders are noted down until quotient becomes zero. Similarly, a fractional part of the number can be converted to other representation by successively multiplying the fractional part by  $b_2$  and noting down the resulting integers. However, in case of fractional part conversion, the conversion may not terminate after the finite number of multiplications.

#### 2.2.1 Decimal to Binary Conversion and Vice Versa

Let us consider the conversion of decimal numbers to binary numbers for example  $(67)_{10}$  is converted to binary representation as follows.

| Division by 2 | Quotient | Remainder |

|---------------|----------|-----------|

| 67÷2          | 33       | 1         |

| 33÷2          | 16       | 1         |

| 16÷2          | 8        | 0         |

| 8÷2           | 4        | 0         |

| 4÷2           | 2        | 0         |

| 2÷2           | 1        | 0         |

| 1÷2           | 0        | 1         |

The resultant binary string is obtained by writing remainders bottom to up (in reverse order). The equivalent binary string for 67 is therefore would be  $(1000011)_2$ . The binary string  $(1000011)_2$  can be converted to decimal number by writing binary numbers as power of 2 as follows

$1 \times 2^{6} + 0 \times 2^{5} + 0 \times 2^{4} + 0 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}$ = 64 + 0 + 0 + 0 + 0 + 2 + 1 = 67

The decimal fraction is converted to binary in a different way. The decimal fraction is multiplied by the base (or radix) of the intended number system and digits so obtained are accumulated. The process is repeated until fraction becomes zero. For example  $(0.8125)_{10}$  is converted to binary number  $(0.1101)_2$  by multiplying the decimal fraction by 2 as follows.

| Multiplication | Result | Integer | Fraction |

|----------------|--------|---------|----------|

| 0.8125 × 2     | 1.625  | 1       | 0.625    |

| 0.625 × 2      | 1.25   | 1       | 0.25     |

| 0.25 × 2       | 0.50   | 0       | 0.50     |

| 0.50 × 2 | 1.00 | 1 | 0 |

|----------|------|---|---|

|          |      |   |   |

Write all the integer parts from top to bottom and obtain the binary number  $(0.1101)_2$ . The fractional binary string  $(0.111)_2$  is converted to decimal fraction as follows

$1 \times 2^{-1} + 1 \times 2^{-2} + 1 \times 2^{-3}$

= 0.5 + 0.25 + 0.125

= 0.875

The power terms of 2 in fractional part always have negative powers.

#### 2.2.2 Decimal to Octal Conversion and Vice Versa

The octal number system is a base 8 system that uses eight digits 0 to 7 to represent any number. Let us consider the example of decimal representation to octal representation conversion. The conversion is performed by successive division operation. Here, the divisor would be 8 as it is base or radix for octal number system. If  $(348)_{10}$  is a decimal number, it is converted to octal representation as follows.

| Division by 8 | Quotient | Remainder |

|---------------|----------|-----------|

| 348÷8         | 43       | 4         |

| 43÷8          | 5        | 3         |

| 5÷8           | 0        | 5         |

The octal number is obtained by writing all remainders bottom to up leading to  $(534)_8$ . The octal representation to decimal number conversion is done with power terms of 8 as follows

$$5 \times 8^{2} + 3 \times 8^{1} + 4 \times 8^{0}$$

=  $5 \times 64 + 24 + 4$

=  $320 + 24 + 4$

=  $(348)_{10}$

Similarly, we can work with fractional parts as discussed earlier for binary numbers. Let us convert  $(0.45)_{10}$  to octal representation by multiplying it by 8 and noting the integer part of the resultant number.

| Multiplication | Result | Integer | Fraction |

|----------------|--------|---------|----------|

| 0.45 × 8       | 3.6    | 3       | 0.6      |

| 0.6 × 8        | 4.8    | 4       | 0.8      |

| 0.8 × 8        | 6.4    | 6       | 0.4      |

| 0.4 × 8        | 3.2    | 3       | 0.2      |

| 0.2 × 8        | 1.6    | 1       | 0.6      |

It can be observed from the above table that it is not possible to terminate the conversion process for  $(0.45)_{10}$  to octal representation in finite number of iteration. Therefore, it is stopped after desired precision. From above table, the resultant octal number for  $(0.45)_{10}$  is obtained as  $(0.34631)_8$  by noting down all integer parts from top to bottom. The conversion of fractional octal number to decimal number is done using negative power terms. For example, let us convert  $(534.28)_8$  to decimal representation.

$5 \times 8^{2} + 3 \times 8^{1} + 4 \times 8^{0} + 2 \times 8^{-1} + 8 \times 8^{-2}$ =  $5 \times 64 + 24 + 4 + 0.25 + 0.125$ =  $(348.375)_{10}$

#### 2.2.3 Decimal to Hexadecimal Conversion and Vice Versa

In hexadecimal number system is a base 16 system. There are sixteen digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. The hexadecimal digit 'A' is equivalent to decimal 10 and digit 'F' is equivalent to decimal 15. The base 10 numbers or decimal numbers can be converted to equivalent hexadecimal number by successively dividing it by 16. Let us consider the example by converting  $(56356)_{10}$  to hexadecimal representation. The calculations are given in the following table. After successive division operations, the remainders are noted down from bottom to up. The resultant hexadecimal number is obtained as  $(DC24)_{16}$ .

| Division by 16 | Quotient | Remainder |

|----------------|----------|-----------|

| 56356÷16       | 3522     | 4         |

| 3522÷16        | 220      | 2         |

| 220÷16         | 13       | 12=C      |

| 13÷16          | 0        | 13=D      |

The reverse conversion i.e. hexadecimal number to decimal can be performed by using power terms of 16 in a similar manner as it is done in other number system. For example,  $(DC24)_{16}$  can be converted to decimal number as follows.

$$D \times 16^{3}+C \times 16^{2}+2 \times 16^{1}+4 \times 16^{0}$$

= 13 × 16<sup>3</sup>+12 × 16<sup>2</sup>+2 × 16<sup>1</sup>+4 × 16<sup>0</sup>

= 13 × 4096+12 × 256+2 × 16 +4 × 1

= 53248+3072+32 + 4

= 56356

We can work with fractional numbers in a similar way as we do in other number systems. The fractional decimal number can be converted to hexadecimal by successively multiplying by 16 and noting the integers in top-down manner. Let us convert  $(0.06640625)_{10}$  to hexadecimal. The resultant hexadecimal number is  $(0.011)_{16}$ .

| Multiplication  | Result | Integer | Fraction |

|-----------------|--------|---------|----------|

| 0.06640625 × 16 | 1.0625 | 1       | 0.0625   |

| 0.0625 × 16     | 1.0    | 1       | 0        |

| 0 × 16          | 0      | 0       | 0        |

#### 2.2.4 BCD Representations

Computer users are more convenient with decimal number system as it is commonly used in real life. The solution of this problem is that users are allowed to work with decimal number system and the decimal numbers are converted to binary numbers while processing them with computers. After completing the processing, the results are converted back to decimal form. All the data is processed or stored with computers in binary coded form. The decimal numbers are stored in registers using binary codes. The conversion of a decimal number to binary coded form is different from converting it to binary number. In binary coded form, each digit of the decimal number is independently converted to binary representation. Each decimal digit is represented with four binary digits. Such a representation is called binary coded decimal (BCD). For example, the number (542)<sub>10</sub> is represented in BCD form as follows

| Decimal number | BCD            |

|----------------|----------------|

| 542            | 0101 0100 0010 |

The alphanumeric character set used in computers contains alphabet, digits, and some special characters. All the elements of alphanumeric character set are represented by binary codes as registers can hold only binary information. American Standard Code for Information Interchange (ASCII) provides a standard seven bits binary codes for alphanumeric character set.

# Check your progress 1

- 1. What is radix or base in number systems?

- 2. The value of radix in octal number system is:

- 3. Convert  $(10101)_2$  to equivalent decimal number.

- 4. Convert  $(A2)_{16}$  to binary.

- 5. Convert  $(A2)_{16}$  to decimal.

- 6. Convert  $(128)_8$  to decimal.

- 7. Convert  $(321)_{10}$  to octal.

- 8. Convert  $(45862)_{10}$  to hexadecimal.

- 9. What is BCD representation?

- 10. How the alphanumeric character set is represented in computer system?

- 11. Convert  $(0.00390625)_{10}$  to hexadecimal.

- 12. Convert  $(0.75)_{10}$  to binary.

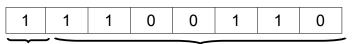

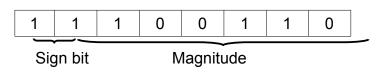

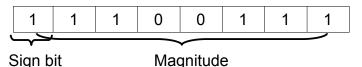

#### 2.3 Negative Number Representation

In conventional mathematics, the signed numbers are represented with the help of plus (+) and minus (-) symbols. However, in digital computers everything including sign of a number must be represented in binary form. All positive numbers and zero can be considered as unsigned numbers but some mechanisms are required for negative number representation. In a simple approach, the sign of a number is represented by a single bit known as **sign bit**. If the value of the sign bit is 0, the number is a positive number or a negative number otherwise. The positive numbers are represented in signed-magnitude form i.e. the most significant bit of the binary string is the sign bit and remaining bits provide the magnitude of the number. For example, +25 is stored in a 8-bit register as follows

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Sign bit Magnitude

However, a negative integer can be represented in three different ways:

- 1. Signed-magnitude representation

- 2. Signed-1's complement representation

- 3. Signed-2's complement representation

The signed-magnitude represented is same as discussed earlier with sign bit set to 1.

For example the number -25 is stored as follows

| 1 | 0      | 0 | 1 | 1 | 0 | 0 | 1 |

|---|--------|---|---|---|---|---|---|

|   | $\sim$ |   |   | ~ |   |   |   |

Sign bit Magnitude

The 1's complement of a negative number is obtained from the signed-magnitude representation of the positive number by complementing its every bit including the sign bit. Therefore, 1's complement of -25 is obtained from +25 as follows

Signed-magnitude representation of +25

0 0 0 1 1 0 0 1

Sign bit Magnitude

Complement each bit to get 1's complement of -25

Sign bit Magnitude

The 2's complement of a number is obtained by adding 1 to the 1's complement representation of the number. It is a two-step procedure given as follows.

1. Invert each bit of the binary string including the sign bit.

2. Treat the result of step 1 as an unsigned integer and add 1.

Usually 2's complement is preferred for arithmetic operations. The 2's complement of - 25 is obtained from its 1's complement as follows.

1. First, obtain 1's complement of -25.

2. Add 1 to 1's complement of -25 to get its 2's complement

#### 2.4 Range Extension

Usually, the same amount of memory is used to store a particular type of data elements irrespective of their values. Often *n* bits are used to store the number even though it may need on *m* bits (n>m). In such case, the bit length is increased. The expansion of bit length is referred to as **range extension**. For example, signed magnitude notation of

+25 is 11001 that actually involves only 5 bits. But if we have to store it in an 8-bit register then we have to increase the length to 8 bits. In signed magnitude notation, the range extension is simple. The additional bit positions are filled with 0's and the sign bit is shifted to the new leftmost position. Let us consider the following example.

| Number | Signed Magnitude | Range Extension | Resultant Number |

|--------|------------------|-----------------|------------------|

|        | Representation   | (8-bit)         |                  |

| +25    | 011001           | 00011001        | +25              |

| -25    | 111001           | 10011001        | -25              |

| Number | Signed Magnitude | Range Extension | Resultant Number |

|--------|------------------|-----------------|------------------|

|        | Representation   | (16-bit)        |                  |

| +25    | 011001           | 000000000011001 | +25              |

| -25    | 111001           | 100000000011001 | -25              |

The signed magnitude representation of +25 or -25 requires 6 bits including sign bit. In order to store it in an 8-bit register, two additional 0's are inserted and sign bit is shifted to the new leftmost position. Similarly for 16-bit memory, 10 additional 0's are inserted and sign bit is shifted accordingly. However, this approach does not work with 2's complement numbers. For such numbers, sign extension is used. In sign extension, the additional bits are filled with sign bit. In other words, additional 0's are inserted for positive numbers, while additional 1's are inserted for negative numbers as follows.

| Number | 2's Complement | Sign Extension  | Resultant Number |  |

|--------|----------------|-----------------|------------------|--|

|        | Representation | (16-bit)        |                  |  |

| +25    | 011001         | 000000000011001 | +25              |  |

| -25    | -25 11100111   |                 | -25              |  |

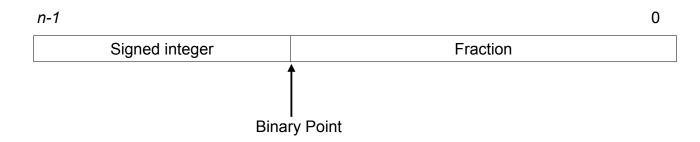

#### 2.5 Fixed-Point Numbers

A number may be integer, fraction, or mixed integer-fraction. Therefore, in addition to the sign of the number, some mechanism is required to separate the integer and fraction parts of a number. A base point or radix point is the mechanism used to identify integer and fraction parts of the number. The position of the radix point is used to decide whether a number is an integer, fraction, or mixed integer-fraction. For binary numbers, the **binary point** is specified by a particular location in the register. If the location of the binary point is fixed i.e. always a specific location to keep the binary point, the representation is known as **fixed-point** numbers. The binary point is a kind of divider between integer and fraction parts. The fixed-point numbers can be given by a tuple  $\langle w, b \rangle$ , where w is the width of the number i.e. the total number bits used for the number and b is the position of binary point from the least significant bit. The notation for a *n*-bit number is illustrated in Figure 2.1. As shown in the figure, the entire number length is divided into two parts: Singed integer and Fraction. Each part has a fixed length. In fact, a number in fixed-point data type is stored as an integer that is scaled by a specific factor. The scaling factor for a number is an implicit value determined by its type. For example, a given number 2.34 can be stored as 2340 with scaling factor 1/1000 or a number 2340000 can be also be represented as 2340 with scaling factor 1000.

Figure 2.1: Fixed-point number representation

The fixed-point numbers are closely related to integer numbers. In fact, integer numbers can be consider a special case of fixed-point numbers, where binary point is at position 0. Therefore, all mathematical operations that a computer can perform with

integers can be applied on fixed-point numbers without any additional hardware. The fixed-point representation of number is therefore simple and efficient. But the system has to compromise with the range of numbers as fixed-point representation can represent only a relatively limited range of numbers.

| Check your progress 2                                            |  |  |  |

|------------------------------------------------------------------|--|--|--|

| 1. What is the value of sign bit for negative numbers?           |  |  |  |

| 2. What is the value of sign bit for positive numbers?           |  |  |  |

| 3. Determine 1's complement of -45.                              |  |  |  |

| 4. Determine 1's complement of +45.                              |  |  |  |

| 5. Obtain 2's complement of -45.                                 |  |  |  |

| 6. What is radix point?                                          |  |  |  |

| 7. How scale factor is determined for a number?                  |  |  |  |

| 8. What is fixed-point number?                                   |  |  |  |

| 9. What would be radix point for integers?                       |  |  |  |

| 10. What is range extension?                                     |  |  |  |

| 11. What is sign extension?                                      |  |  |  |

| 12. Perform range extension for +18 and -18.                     |  |  |  |

| 13. Perform sign extension for +18 and -18.                      |  |  |  |

| 14. What is the major limitation of fixed-point numbers?         |  |  |  |

| 15. How integer numbers are special case of fixed-point numbers? |  |  |  |

#### 2.6 Floating-Point Numbers

The fixed-point numbers can be processed at a faster rate with the available capabilities of the system. But at the same time, only a small range of numbers can be provided with this representation. To overcome the limitations of the fixed-point numbers, there is another approach of representing signed numbers known as floating-point. It represents a number in two parts: mantissa (*m*) and exponent (*e*). The mantissa is a fixed-point number and exponent specifies the location of base/radix point. It is similar to scientific

notation, where a number with base *b* is written as  $m \times b^e$ . For example, a decimal number 589.621 is written as  $0.589621 \times 10^3$  in scientific notation. It can be written in floating-point representation as follows

| Mantissa  | Exponent |  |

|-----------|----------|--|

| +0.589621 | +3       |  |

Both mantissa and exponent are stored in registers separately. A binary number is written in the same way with base 2. Both mantissa and exponent use 2's complement format. For example, a binary number  $(+1011.01)_2$  is written as

| Mantissa | Exponent |  |

|----------|----------|--|

| 00000101 | 000011   |  |

where mantissa and exponent are 8-bit and 6-bit components respectively. If the most significant bit of the mantissa is nonzero then the number is called to be normalized.

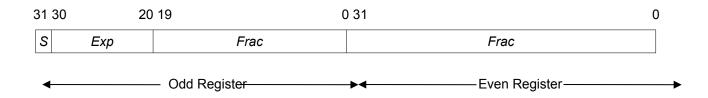

#### 2.7 IEEE Floating-Point Standard

A working committee of IEEE has developed three standards of floating-point representations known as: **single precision**, **double precision**, and **extended precision**. The single precision numbers require a 32-bit word whose representation is shown in Figure 2.2.

| 31 3 | 30             | 23 22 |                 | 0 |

|------|----------------|-------|-----------------|---|

| S    | Exponent (exp) |       | Mantissa (frac) |   |

#### Figure 2.2: Single precision floating-point representation

In the Figure 2.2, *S* represents the sign bit, *exp* is the exponent, and *frac* represents the mantissa of the number. The mantissa part has 23 bits, exponent takes 8 bits, and remaining 1 bit is occupied by sign part. The sign bit is 0 for a positive number and 1 if negative. The number is normalized so that the binary point is at right of the

leading 1 i.e. the mantissa is always 1.xxxxxx...xxx in the normalized form. Because leading bit is always 1, there is no need to store it. It is an implied bit. Therefore, effectively the mantissa part has 24 bits. For zero, a special representation is used with all 0's both for mantissa and exponent fields as well as sign bit. In IEEE standard floating-point numbers, the exponent part does not use sign-magnitude, 1's complement, or 2's complement format. It uses a **biased representation**, which is simply the binary representation of E+127, where E is the actual exponent and the number 127 is called the exponent bias. The actual exponent is obtained by subtracting the exponent bias from the stored exponent. Mathematically, the above representation gives

The dynamic range of single precision floating-point numbers goes from  $1.175 \times 10^{-38}$  to  $3.4 \times 10^{-38}$ .

Although single precision floating-point numbers are adequate for the most of the applications, there is another commonly used alternative is double precision floating-point numbers. The double precision numbers use 64-bit words. However, arrangement is similar to the single precision floating point numbers. Only the width of the fields and exponent bias are different. The arrangement of different fields in the double precision floating-point representation is shown in Figure 2.3. It uses two 32-bit registers designated as odd and even registers to make it 64-bit numbers.

Figure 2.3: Double precision floating-point representation

Mathematically, the above representation gives

- 1<sup>S</sup>·2<sup>exp-1023</sup>.1.frac

where *S* is the sign bit, *exp* is 11-bit exponent, and *frac* is 52-bit mantissa. The mantissa takes 32 bits from even register and 20 bits from odd register. The dynamic range of double precision numbers varies from  $2.2 \times 10^{-308}$  to  $1.7 \times 10^{308}$ .

The third floating-point representation known as extended precision floating-point numbers is not very different from the previous two representation but requires 80-bit word. Like other two notations, it uses 1 bit as sign bit, 15 bits as exponent, and 64 bits for mantissa. Unlike single and double precision, the leading bit in extended precision is not generally hidden. As compared to fixed-point numbers, the arithmetic operations with the floating-point numbers are complex to perform and require complex hardware and longer execution time. However, the most of computing devices use floating-point arithmetic as flexible base point is required in scientific operations.

#### Check your progress 3

- 1. Is mantissa a fixed-point number?

- 2. What is exponent in floating-point numbers?

- 3. Which number representation is used for mantissa and exponent?

- 4. How do you identify a normalized number?

- 5. List the standards defined by IEEE for floating-point numbers.

- 6. How many bits are required for single precision floating-point numbers?

- 7. What is biased representation?

- 8. How many bits are required for extended floating-point numbers?

#### 2.8 Summary

Data representation refers to the form in which data can be stored, processed, and transmitted. There are different number systems that are used to represent numbers in different forms. For digital computers, the binary number system is the most useful. But users are more convenient with decimal number system. Therefore, numbers are

needed to convert from one system to another. The numbers in different number systems can be converted to other number systems using Radix Conversion method. All the data is processed or stored with computers in binary coded form. The decimal numbers are stored in registers using binary codes. The conversion of a decimal number to binary coded form is different from converting it to binary number. In binary coded form, each digit of the decimal number is independently converted to binary representation. Each decimal digit is represented with four binary digits. Such a representation is called binary coded decimal (BCD). American Standard Code for Information Interchange (ASCII) provides a standard seven bits binary codes for alphanumeric character set.

In conventional mathematics, the signed numbers are represented with the help of plus (+) and minus (-) symbols. However, in digital computers everything including sign of a number must be represented in binary form. All positive numbers and zero can be considered as unsigned numbers but some mechanisms are required for negative number representation. In a simple approach, the sign of a number is represented by a single bit known as sign bit. If the value of the sign bit is 0, the number is a positive number or a negative number otherwise. However, a negative integer can be represented in three different ways: Signed-magnitude representation, Signed-1's complement representation, Signed-2's complement representation.

The computers store the numbers in registers. All the information related to numbers such as sign, base point, and magnitude, etc. is stored in binary form. Often n bits are used to store the number even though it may need on m bits (n>m). In such case, the bit length is increased. The expansion of bit length is referred to as range extension. There are two prominent notations for numbers: fixed-point and floating-point numbers. The floating-point arithmetic is preferred in digital computers despite the higher complexity due to flexible base point. A number may be integer, fraction, or mixed integer-fraction. Therefore, in addition to the sign of the number, some mechanism is required to separate the integer and fraction parts of a number. A base point or radix point is the mechanism used to identify integer and fraction parts of the number, is an integer, fraction, or mixed integer-fraction. If the location of the base point is fixed, the

representation is known as fixed-point numbers. The fixed-point numbers can be processed at a faster rate with the available capabilities of the system. But at the same time, only a small range of numbers can be provided with this representation. To overcome the limitations of the fixed-point numbers, there is another approach of representing signed numbers known as floating-point. A working committee of IEEE has developed three standards of floating-point representations known as: single precision, double precision, and extended precision.

#### **Review Questions**

- Q.1 Convert following numbers to binary: (295)<sub>10</sub>, (5482)<sub>10</sub>, (763)<sub>10</sub>, and (4169)<sub>10</sub>.

- Q.2 Convert following numbers to decimal:  $(1100)_2$ ,  $(101101)_2$ ,  $(10010)_2$ , and  $(101110)_2$ .

- Q.3 Convert following numbers to hexadecimal:  $(78956)_{10}$ ,  $(89645879)_{10}$ ,  $(84845684)_{10}$ ,  $(24242424)_{10}$ , and  $(1816181615)_{10}$ .

- Q.4 Convert following numbers to octal: (1100)<sub>2</sub>, (101101)<sub>2</sub>, (10010)<sub>2</sub>, and (101110)<sub>2</sub>.

- Q.5 Write the following numbers in BCD form: (745)<sub>10</sub>, (8632)<sub>10</sub>, and (9100)<sub>10</sub>.

- Q.6 Write following numbers in 1's complement: +47, -95, +63, -81.

- Q.7 Write following number in 2's complement: +47, -95, +63, -81.

- Q.8 Convert following numbers to binary: (5462)<sub>8</sub>, (2534)<sub>8</sub>, (163)<sub>8</sub>, and (15)<sub>8</sub>.

- Q.9 With the help of suitable diagrams explain the single-precision and doubleprecision floating-point number representation. Differentiate both representations.

- Q.10 Why rage extension is required and how it is performed?

- Q.11 Explain different representations for negative numbers with suitable examples.

# **Unit 3: Instruction Sets**

#### Structure

- 3.0 Introduction

- 3.1 Objectives

- 3.2 Instruction Formats

- 3.3 Instruction Types

- 3.4 Addressing Modes

- 3.5 Programming Considerations

- 3.6 Summary

**Review Questions**

#### **3.0 Introduction**

The digital computers perform operations as directed with the set of instructions. The instructions or machine instructions or computer instructions are the commands that control the operations of a computer. A computer instruction is a binary code that instructs the computer to execute specific operations. The instructions and data are stored together in the computer memory. The CPU reads the instruction from the memory, interprets it, and performs the desired operation on the relevant data fetched from the memory. A set of instructions is used to control the sequence of operations. Each processor has its own collection of instructions that it can recognize and execute. Such a set is called processor's instruction set.

An instruction is a group of bits that is divided into multiple fields. Each field provides specific information such as operation type, operands, and references to the next instructions, etc. Different fields of the instructions are loaded in registers. Each instruction must contain at least two types of information, the operation to perform and data elements required during the operation. The operation to be performed is provided in a field known as **op-code** and addresses of operands are given in **address** field. The op-code represents operations such as add, subtract, multiply, divide, read, and write, etc. There may be two types of addresses, source and destination. The source address field operands, while destination address field is used to write the result of the operation. Sometimes, the field is used as source and destination. The instructions can be divide into different categories depending on the number of operands involved. As machine instruction are in binary format, it is difficult for programmers to work with machine instructions. Therefore, it is a general practice to use symbolic representation for the machine instructions. Although it is possible to write computer programs directly in machine language, but the modern programmers rarely use the machine instructions to write the programs. The most of the programmers work with high level languages.

#### 3.1 Objectives

After the completion of this unit, the students will be able

- 1. To understand the instructions of computer systems.

- 2. To understand instruction formats.

- 3. To understand use of addresses and registers in instructions.

- 4. To learn different types of instructions.

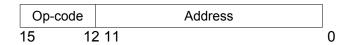

#### **3.2 Instruction Formats**

In order to perform a given task, the digital computers are provided a sequence of instructions. Each instruction specifies a particular operation to perform on one or more data elements. A computer instruction is a binary string with codes for both operation and data. For each microprocessor, there is a set of instructions. The most of the instruction sets contain instructions in multiple formats. The simple form of instruction has two fields, op-code and address as shown in Figure 3.1. The figure shows a 16-bit instruction formats. The four most significant bits represent op-code and other bits provide address for operands. The instruction set for such a processor can have at most 16 instructions as 4 bits are used for op-code field. When instructions are loaded from the memory, the op-code and operands are stored in registers. The **accumulator (AC)** is the most rigorously used register. There are some operations that do not need any operands from memory. Clear the AC, complement the AC, and increment the AC, etc. are some examples of such operations. The instructions for such operations do not need address field.

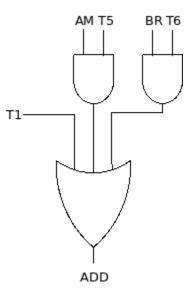

Figure 3.1: Instruction format having two fields

It is a general practice to use a symbolic representation for machine instructions. The op-codes are given by abbreviations known as **mnemonics**. Some examples of mnemonics are given here.

| LOAD | Load data from memory |  |

|------|-----------------------|--|

| ADD  | Add                   |  |

| SUB  | Subtract              |  |

| MUL  | Multiply              |  |

| DIV  | Division              |  |

| STOR | Store data to memory  |  |

| MPY  | Multiply              |  |

Symbols are also used to represent the operands in an instruction. The symbols such as R, A, X, and Y, etc. may represent the contents of registers, memory location, or data elements. There are different types of arithmetic operations involving different number of operands. The **unary** operations require only one operand, while **binary** operations need two operands. These operands are called as **source operands**. In addition to operands, one location (register or memory) is required to place the result of the operation. It is called as **destination operand**. There are some other operations mostly non-mathematical that can be performed without any operand. Therefore, depending on the number of source operands and destination operands, the number of addresses used in an instruction may vary from one to three. Based on the number of addresses, the instructions can be classified as **zero-address**, **one-address**, **twoaddress**, and **three-address** instructions. Some examples of instructions written with symbolic representation are given in the Table 3.1.

The stack data structure loads and retrieves data elements in last-in-first-out fashion. The location of the stack is usually known or at least top two elements are stored in predefined registers. The *pop* operation retrieves top element from the stack.

Therefore, the pop operation do not need any operand as location of the top of stack is available. As discussed earlier, clear AC and increment AC are other operations for which no operands is required. Thus, the instructions for such operations are zero-address instructions.

| Ins  | truction | Туре          | Comment                                   |

|------|----------|---------------|-------------------------------------------|

| LOAD | D        | One-address   | Load AC from location D                   |

| STOR | Y        | One-address   | Load content of AC to location Y          |

| SUB  | В        | One-address   | Subtract B from AC and store result to AC |

| ADD  | В        | One-address   | Add B and AC and store result to AC       |

| MOVE | B, A     | Two-address   | Load content of A to location B           |

| SUB  | Υ, Β     | Two-address   | Subtract B from Y and store result to Y   |

| ADD  | С, В     | Two-address   | Add B and C and store result to C         |

| MPY  | Υ, Β     | Two-address   | Multiply B with Y and store result to Y   |

| SUB  | Y, A, B  | Three-address | Subtract B from A and store result to Y   |

| ADD  | Y, C, B  | Three-address | Add B and C and store result to Y         |

| MPY  | Y, C, B  | Three-address | Multiply B with C and store result to Y   |

| DIV  | Y, C, B  | Three-address | Divide C by B and store result to Y       |

Table 3.1: Some Examples of Instructions

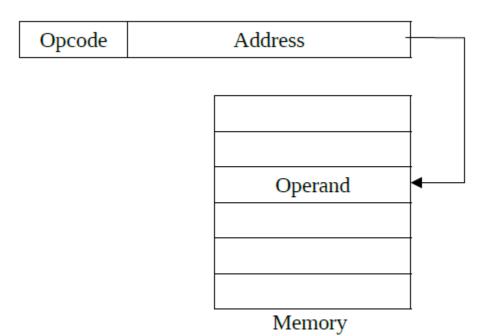

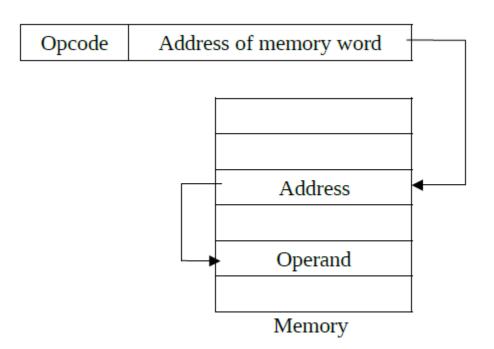

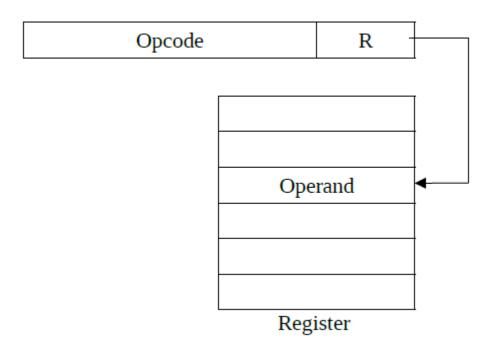

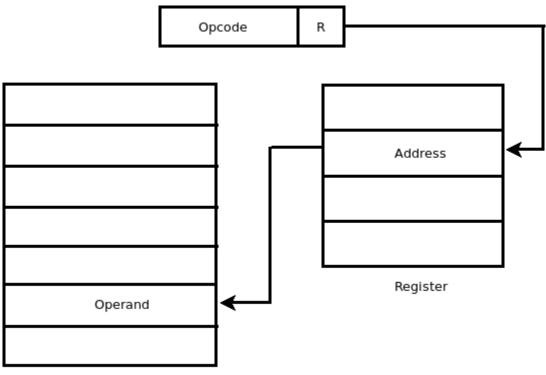

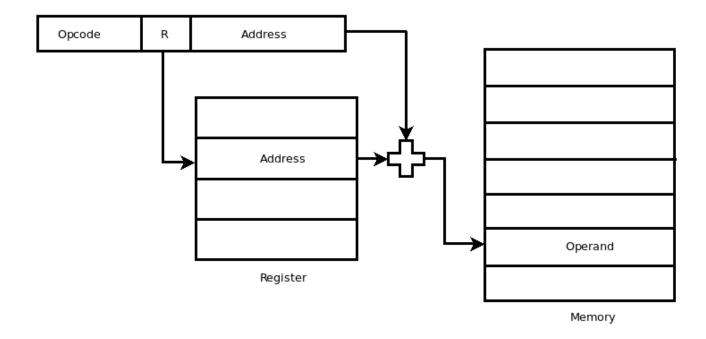

There are different types of operands such as number, character, logical data, and address. The second field in the instruction may not contain addresses but actual operands. If second field provides the operands, it is an instruction with **immediate operands** and it is called an **immediate instruction**. If the second field contains address, there are further two possibilities. The address either specifies the location of the operand itself or it provides the location that contains the address of the operand. If address field provides the memory location of the operand itself, it is known as **direct address** otherwise in case it specifies another address then it is called **indirect address**. To indicate whether it is a direct or indirect address, the most significant bit of the instruction designated as I is reserved as shown in Figure 3.2. The value of bit I is 0 for direct address and 1 for indirect address.

| Ι  | Op-<br>code | Address |

|----|-------------|---------|

| 15 | 12          | 11 0    |

Figure 3.2: Instruction format having three fields

#### Check your progress 1

- 1. What are different fields in instruction format?

- 2. What is the use of opcode field of instruction format?

- 3. Classify the types of instructions based on number of addresses.

- 4. What is immediate instruction?

- 5. What is the difference between direct address instruction and indirect address instruction?

#### 3.3 Instruction Types

The basic instruction set of a computer contains three types of instructions: **registerreference** instruction, **input-output** instruction and **memory-reference** instruction. Register-reference instructions are recognized by I=0 and op-code 111. For input-output instructions I=1 and op-code 111 are used. For memory-reference instructions I may be 0 or 1 and op-code varies 000 through 110. There are a number of instructions in the instruction set that can be further divided into different categories depending on the kind of operation they perform. There are some basic operations for which there should be instructions in instruction set. If all such instructions are there in the instruction set, the programmers may write programs to evaluate any function. Such an instruction set is said to be complete. On this basis, the instructions can be divided into following categories.

#### 3.3.1 Data Transfer Instructions

The data transfer are the most fundamental instructions of any instruction set in a computer system. The majority of operations need data elements to transfer from

memory to register, register to memory, or register to register. A data transfer instruction must have a source location, a destination location, length of the data to transfer, and addressing mode. There could be different variants of the data transfer instructions depending on whether operand is a register or memory. The data length is usually 8, 16, 32, or 64 bits. The length of data to be transferred also lead to different variants of instructions. If source and destination locations both registers, then data transfer operands are simple as registers are internal to the processor. However, if operands are memory locations then data transfer operations are comparatively complex. Some examples of data transfer instructions are given in Table 3.2.

| Instruction | Operation | Description                                                           |

|-------------|-----------|-----------------------------------------------------------------------|

| LD          | Load      | Data transfer from memory to floating point register                  |

| LDR         | Load      | Data transfer from floating point register to floating point register |

| ST          | Store     | Data transfer from register to memory                                 |

| STD         | Store     | Data transfer from floating point register to memory                  |

Table 3.2: Examples of logical instructions

#### **3.3.2 Arithmetic Instructions**

The instructions for basic arithmetic operations such as addition, subtraction, multiplication, and division are included in the instruction set of the most of the computers. These instructions are available for both fixed point and floating point numbers. All the basic arithmetic operations need two operands. Therefore, usually two-address or three-address instructions are needed for such operations. Sometimes one-address instructions may also be used for such operations, where one operand is inherently available and second operand is explicitly given. In addition, there are other arithmetic instructions that need single operand. Some of the single operand arithmetic operations are as follows.

Increment: Add 1 to the operand

Decrement: Subtract 1 from the operand

Absolute: Take absolute value of the operand

Negate: Negate the operand

Some examples of arithmetic instructions are given in Table 3.3.

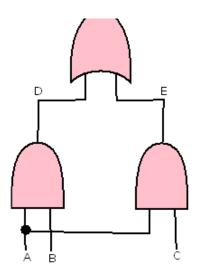

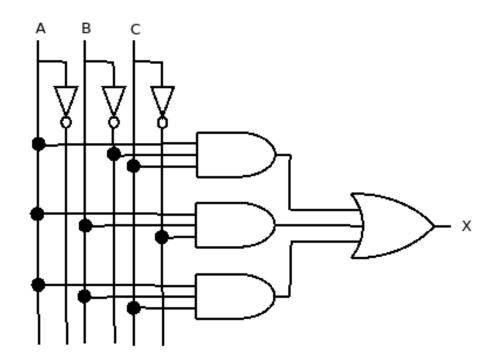

#### **3.3.3 Logical Instructions**

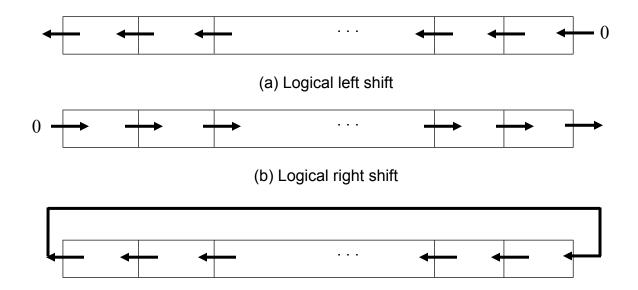

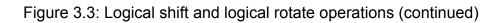

Logical instructions manipulate bits or binary numbers. A number of logical instructions are part of the instruction set of the most of the computers. The operations that work on individual bits of a binary number are called the bitwise logical operations. The widely used bitwise logical instructions are **AND**, **OR**, **NOT**, and **XOR**, etc. The NOT operation works with one operand, while AND, OR, and XOR operations require two operands. Shift and rotation are other important logical operations. There are two types of logical shift operations: **logical left shift** and **logical right shift**. The logical left shift operation shifts the bits of a binary number from the least significant location towards the most significant location is just lost or discarded. The logical right shift operation shifts the bits from the most significant location towards the least significant location. The new 0s are inserted at the most significant position and bit coming out of the least significant location.

| Instruction | Operation   | Description                                                      |  |

|-------------|-------------|------------------------------------------------------------------|--|